# 低溫複晶矽製造技術之動向

# The Technology of Low Temperature Polysilicon Thin Film Transistor

陳志強 Chih-Chiang Chen

在眾多琳琅滿目的新世代顯示技術中,低溫複晶矽薄膜電晶體扮演舉足輕重的角色,由於低溫複晶矽具有較佳的特性,且製程與傳統非晶矽截然不同,因此需開發的製程較多,諸如複晶矽薄膜結晶、閘極絕緣層、離子植入、離子活化等等,雖然待開發的製程繁雜,但實際製程開發都是以提升元件特性及電路積集度為首要目標。本文將針對低溫複晶矽製造技術之動向與近況做一簡單的介紹。

Low temperature polycrystalline silicon (LTPS) technology has been the most promising method to manufacture next generation display. Compared to the conventional amorphous silicon TFTs, the LTPS has higher mobility and smaller design rule. To realize system on panel, the polysilicon crystallization, gate insulator, ions doping and activation were widely adopted in active matrix array and integrated peripherals circuit. Using those technologies we can achieve better device characteristic and more system integrated. In this article we will introduce the technology of low temperature polysilicon TFTs.

# 一、前言

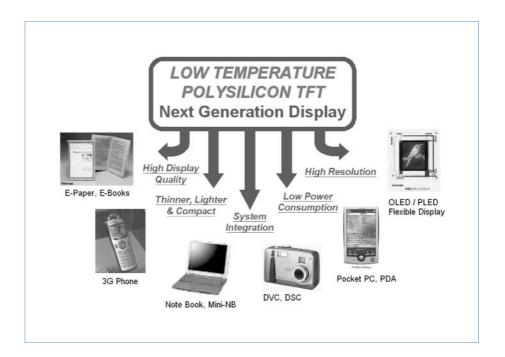

隨著數位時代來臨,平面顯示器應用領域從可 攜式中小型產品邁向資訊用與視訊應用的大型面 板,傳統的液晶顯示面板已不敷使用。相較於非晶 矽 (amorphous silicon) 薄膜電晶體較低的載子移動 率,低溫複晶矽 (low temperature poly-silicon, LTPS) 技術可將電子移動率提升兩百倍以上甚至接近於單 晶矽,且對於元件縮小化、面板的開口率、畫面品 質與解析度上有絕對的優勢。如圖 1 顯示,下一世 代資訊電器強調輕薄短小與高畫質,低溫複晶矽充 分滿足消費者的需求,特別當解析度大於 130 ppi (pixels per inch) 時,非晶矽容易受限於外貼驅動 IC 腳位間距面積,低溫複晶矽內建整合電路的優點, 克服了這類的問題。再者低溫複晶矽提供互補式薄 膜電晶體技術,除了具有較佳的顯示效果外,更具 有廣闊的設計窗口。表 1 顯示低溫複晶矽薄膜電晶 體顯示器近年來之進展,可以清楚地發現除了將驅 動電路整合於玻璃外,系統積集度的提升與附加功 能的加值性,使面板同時具備有窄框化 (narrow

圖 1 低溫複晶矽顯示技術之應用。

frame size) 與高品質的特性,因此採用低溫複晶矽 做為主動載具絕對是未來的趨勢<sup>(1)</sup>。

# 二、低溫複晶矽的技術動向

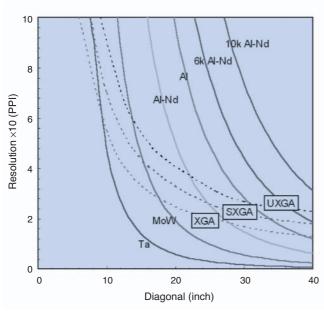

低溫複晶矽搭配高電漿密度的乾蝕刻製程與精準的微影技術,可達到 1.5 µm 面板設計準則,相較傳統的非晶矽薄膜電晶體小了許多,也因為如此,其具有窄框化、較高開口率與解析度,藉此可減少額外半導體的零件數並縮小外部電路基板面積。一般而言,驅動 IC 約佔周邊成本的六分之一,以 XGA 解析度為例,傳統非晶矽面板需要 11 顆驅動 IC (Data:Ch384×8 與 Scan:Ch258×3),而低溫複晶矽只需 4 顆 IC,甚至更少。低溫複晶矽成功地實現低成本化與小型輕量化,再者,內建驅動電路使得外部訊號接線減少,大幅降低電磁干擾的影響,並提高了因外貼驅動 IC 所導致的良率下降與可靠度,增加面板的使用壽命。

在耗電量方面,由於高開口率的優點,有效的減少背光源與系統的負擔,並且配合反射式 (reflective) 與半透式 (transflective) 應用,加上畫素內建記憶體 (SRAM 或 DRAM) 架構,以節省資料線的功率消耗,也可以利用多重格式 (multiformation) 或多重解析度 (multi-resolution) 的驅動系

統,同時達到省電與功能多樣化的優點。如表 1 所示,Sharp 公司已成功地開發出整合 8-bit Z80 CPU 於玻璃面板上,將低溫複晶矽的優點發揮得淋漓盡致,完成系統面板 (system on panel, SOP) 相信指日可待。

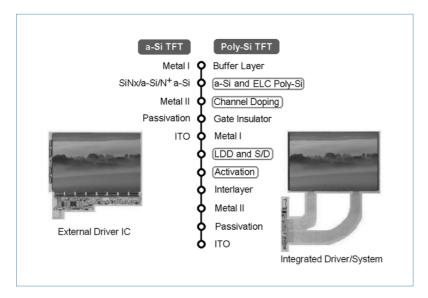

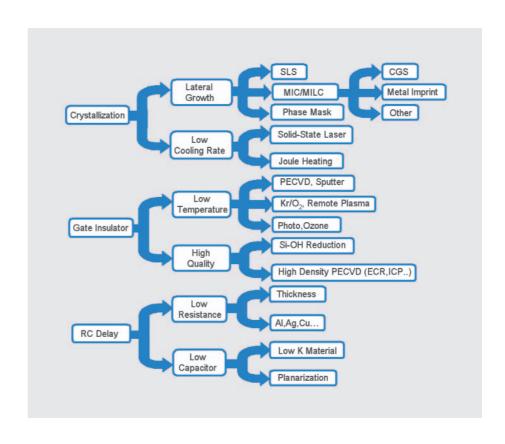

然而低溫複晶矽技術並非沒有缺點,由於複晶矽天生的晶粒缺陷容易造成漏電流的增加與臨界電壓的漂移,使得面板顯示均匀性不佳,特別當電晶體尺寸縮小時將更加地嚴重,因此利用輕汲極摻雜(lightly doped drain)與通道摻雜(channel doping)將薄膜電晶體的漏電流與臨界電壓作精確的控制勢將無可避免。如圖2所示,雖然低溫複晶矽有較佳的特性與整合電路的優點,但相較非晶矽面板的四至五道製程,低溫複晶矽薄膜電晶體八至九道製程足足比非晶矽多了一倍,再加上部份關鍵製程仍待開發,其技術與成本上相對較高(如圖3所示),與非晶矽面板在市場佔有率與良率的控制上的差距依然存在,因此不斷追求面板附加價值與創意,方是低溫複晶矽未來開發重點。

# 三、Precursor 薄膜技術

薄膜電晶體的心臟-複晶矽一直是重要技術瓶 頸之一,而非晶矽 precursor 的成膜好壞直接影響

年份 內 容 公司 1888 · Discover LC material 1981 Hitachi · Low temperature poly-Si TFT 1984 Seiko • High temperature poly-Si TFT 1994 Xerox • a-Si display with poly-Si Driver 1995 Seiko Epson · Pixel array and Drivers Separately 1996 Sanyo • 2.5-inch LTPS AMLCD 1997 Toshiba • 12.1-inch LTPS AMLCD 1998 Sharp • 2.6-inch CGS AMLCD Toshiba • 15-inch LTPS AMLCD Sanyo • 2.4 inch LTPS AMOLED 1999 • 12.1 LTPS AMLCD with 5 Mask Process LG-Philips • 0.7-inch SUFTLA Flexible AMLCD Seiko Epson • 2-inch LTPS AMLEP Toshiba • 2.1-inch LTPS AMLCD with SRAM Integrated 2000 Sanyo • 2.1-inch LTPS AMLCD with SRAM Integrated • 2.1-inch LTPS AMLCD with High-Accuracy DA Toshiba Converter and Amplifier Integrated 2001 • 2.85-inch QCIF AMLEP Sony 13-inch LTPS AMOLED Mitsubishi • 2.1-inch LTPS AMLCD with DRAM Integrated Sharp • 8-bit Z80 CPU on Glass • 8.4-inch LTPS Flexible AMLCD Toshiba • 17-inch LTPS AMLEP 2002 Seiko Epson • 2.1-inch SUFTLA Flexible AMOLED • 3.8-inch LTPS LCD with Integrated Interface Sony Circuit • 1.5-inch Flexible AMLCD

表 1. 低溫複晶矽薄膜電晶體顯示器之進 展。

圖 2. 低溫複晶矽薄膜與非晶矽流程之差異性。

圖 3. 低溫複晶矽之關鍵製程技術。

到後續複晶矽的形成與元件特性。為了達到大面積 與均匀性的要求,電漿輔助化學氣相沈積 (plasma enhanced chemical vapor deposition, PECVD) 廣泛地 使用於非晶矽與複晶矽的製程中 (如表 2 所示)。但 由於 PECVD 所成長出的非晶矽其氫含量較高 (約 8-15%),容易因雷射所造成的氫解離而產生薄膜 氫爆 (ablation),需做額外的高溫烘烤處理將多餘 的氫去除。此外,為了降低熱循環與簡化製程步 驟,可採用室溫或低於 100°C 的物理氣相沈積 (PVD) 方式濺鍍非晶矽薄膜,但由於濺鍍時所造成 的非晶化,可配合雷射照射的方式將這些非晶化薄 膜再結晶成為複晶矽。以物理氣相沈積方式形成的 複晶矽薄膜具有低溫與均匀性佳的優點,其所需的 電射結晶能量較一般傳統的高。另外採用濺鍍成膜 具有非常低的氫含量,具有方向性、高致密性、高 純度與低雜質濃度,相對的能有效減少通道中的晶 粒缺陷。

由於一般物理氣相沈積所成長出的非晶矽結構較緻密,再加上成長溫度低,不需使用有毒或氣體來源,基於安全與效能考量,物理氣相沈積將成為未來低溫薄膜技術的趨勢。另外有別於電漿輔助化學氣相沈積的成膜原理,觸媒式化學氣相沈積(catalytic chemical vapor deposition, Cat-CVD)利用加熱的觸媒(如鎢線),瞬間高溫使得原料分解並直接生成複晶矽薄膜,其系統簡單且大面積沈積容易,並可控制成長複晶矽薄膜之氫含量,其製程溫度約兩百至五百度之間,這類觸媒式化學氣相沈積成膜方式頗受低溫製程矚目(如表2所示)。

表 2. Precursor 薄膜技術分類。

| 成膜方式       | 材質           | 厚度 (nm) | 成膜溫度 (°C) | 參考資料                     |

|------------|--------------|---------|-----------|--------------------------|

| Cat-CVD    | Polysilicon  | 150     | 500       | R. E. I. Schropp, MRS 00 |

| PECVD      | Amorphous-Si | 50      | 380       | T. Tamura, MRS 00        |

| PECVD      | Amorphous-Si | 30      | 110       | D. P. Gosain, JJAP 00    |

| Sputtering | Amorphous-Si | 100     | 200       | T. Serikawa,EDL 02       |

| Sputtering | Amorphous-Si | 90      | 300       | G. K. Giust, ED 00       |

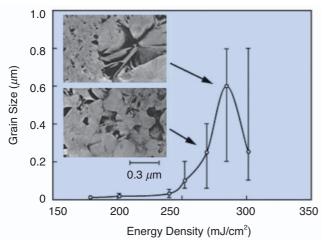

圖 4. 雷射能量密度與複晶矽晶粒尺寸之相關性 (資料來源: Fujitsu)。

# 四、複晶矽結晶技術

1960 年 Maiman 發表紅寶石雷射以來,至今已有半個世紀了,隨著技術的演進,雷射的應用也廣泛的遍及各產業,小至近視矯正,大到做為太空武器,無不見到其蹤跡。近年來由於平面顯示器的蓬勃發展,雷射應用於低溫複晶矽薄膜電晶體也應運而生。早期的低溫複晶矽是採用固相結晶 (solid phase crystallization, SPC) 的方法,但高達六百度高溫與二十四小時以上長時間製程下,必須採用熔點較高且成本較玻璃貴的石英基板,再加上石英基板尺寸的限制,面板大約僅有二至四吋,因此只能發展小型面板。鑑於傳統成膜方式溫度過高的缺點為人所詬病,低溫複晶矽利用雷射結晶複晶矽薄膜降低了熱循環並提高薄膜品質,雷射結晶化 (laser

crystallization)的方式將製程溫度降到室溫,因此大型化面板尺寸才得以實現。為了有效降低熱循環與減少對基板的傷害,一般應用於結晶複晶矽薄膜多採用短波長的準分子雷射,如 XeCl (308 nm)、KrF (248 nm) 雷射,應用於量產的商品上多採用效率與穩定性較佳的 XeCl 雷射,目前低溫複晶矽的製造大廠如 Toshiba、Sanyo、Sony等都是採用XeCl 雷射結晶的方式。而 Sharp 採用鎳金屬誘發側向結晶 (metal-induced lateral crystallization, MILC)的方式,搭配準分子雷射與 gettering 製程形成連續矽晶界 (continuous grain silicon, CGS) 薄膜,也是不錯的選擇。

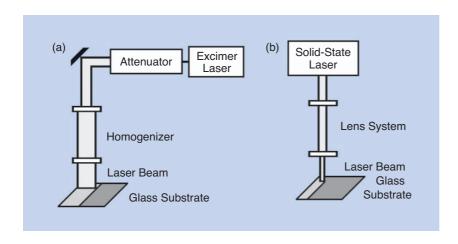

由於準分子雷射是一種脈衝式雷射,因此脈衝 的特性諸如雷射光束的波型 (beam profile)、掃描的 重疊次數 (overlap)、雷射能量密度、能量的穩定性 (pulse to pulse stability) 與外在環境如基板溫度、環 境氣份等(如圖 4),都會直接的影響到複晶矽薄膜 品質。而為了達到較大的晶粒尺寸 (grain size),通 常希望複晶矽成膜於超級側向成長區域 (super lateral growth, SLG), 然而 SLG 的製程窗口通常不 大,因此雷射設備的穩定性相當重要。另外,雷射 光束經過光學系統的調變後其雷射長度並不長,應 用於面積大時必須採取多道雷射掃描的方式 (如圖 5(a)),因此在大面積基板時其均匀性與產能成為雷 射應用的最大致命傷。另外,雖然準分子雷射具有 高能量與效率,但是雷射壽命較短加上設備成本昂 貴,是低溫複晶矽製造商的沈重負擔。為了達到快 速且品質佳的目的,另一種常用於薄膜結晶為固態 雷射 (solid-state laser),有摻釹釔鋁石榴石 (yttrium

圖 5.

(a) 準分子雷射系統示意圖,(b) 固體 雷射雷射系統示意圖。

表 3. 複晶矽結晶技術分類。

| 雷射種類                                 | 波長 (nm)               | 操作方式     | 複晶矽晶粒大小<br>(μm) | 薄膜電晶體<br>移動率<br>(cm²/V·S) | 參考資料                         |

|--------------------------------------|-----------------------|----------|-----------------|---------------------------|------------------------------|

| XeF                                  | 351                   | 脈波       | _               | 100                       | CD. Kim, ED 96               |

| XeCl                                 | 308                   | 脈波       | 1.5             | 236                       | N. Ibaraki, SID 99           |

| KrF                                  | 248                   | 脈波       | _               | 329                       | H. Zhang, EDL 92             |

| Nd:YAG                               | 532 (2ω)              | 連續波      | $1.5 \times 20$ | 300                       | A. Hara, IEDM 00             |

| Nd:YAG                               | 532 (2ω)              | 脈波       | 1 × 2           | 202                       | T. Ogawa, EuroDisplay 99     |

| Nd:YVO <sub>4</sub> (CLC)            | 532 (2ω)              | 連續波      | 3 × 20          | 566                       | F. Takeuchi, IDMC 02         |

| Nd:YVO <sub>4</sub>                  | 532 (2ω)              | 脈波       | 2×100           | 510                       | Y. Helen, Thin Solid Film 01 |

| Ar <sup>+</sup>                      | 514                   | 連續波      | _               | 130                       | K. Masumo, AMLCD 97          |

| Ar <sup>+</sup> + ELA                | 514 + 248             | 脈波+連續波   | 100             | _                         | G. Andra, Thin Solid Film 98 |

| MILC + XeF<br>(L-MILC)               | 351                   | 脈波       | _               | 180                       | D. Murley, AMLCD 00          |

| MILC + ELA<br>(CGS)                  | 308                   | 脈波       | 連續晶界            | 260                       | N. Makita, AMLCD 00          |

| ELA + Nd:YVO <sub>4</sub><br>(SELAX) | $308 + 532 (2\omega)$ | 脈波 + 連續波 | 0.4 × 100       | 460                       | M. Hatano, SID 02            |

| XeCl + Reticle Mask<br>(SLS)         | 308                   | 脈波       | 局部單晶            | 461                       | M. A. Crowder, EDL 98        |

aluminum garnet, Nd:YAG) 雷射、摻釹釩酸釔 (yttrium ortho vanadate,  $Nd:YVO_4$ ) 雷射與氫離子  $(Ar^{+})$  氣體雷射等 (如表 3 所示),由於這類雷射具有高重複率與相當窄的半高波寬,相較準分子雷射具有可靠、耐用、價廉且維護成本低的優點。

過去由於固態雷射尚未臻成熟,實際應用於低溫複晶矽薄膜電晶體製程上有困難,近來二極體激發式固態雷射 (diode pumped solid state laser, DPSS) 倍受關注,其迅速發展也帶動了固態雷射的發展。由於準分子雷射價格昂貴,可以藉由倍頻的技術產生價格較便宜的短波長雷射,常見的方式乃是利用二極體激發式固態雷射或其他倍頻技術,將原本波長 1060 nm 產生二次諧振,使頻率增加兩倍 (532 nm),利用這種二極體激發式固態雷射可達到 1%的高功率穩定性。使用倍頻二極體激發式固態雷射可以提供比氫離子氣體雷射高的連續光輸出 (如圖5(b)),相對於準分子雷射與氣體雷射有較佳穩定性、效率與可靠性,目前採用的廠商有 Fujitsu 與Hitachi 等。

為了達到系統整合面板的境界,更高的載子移

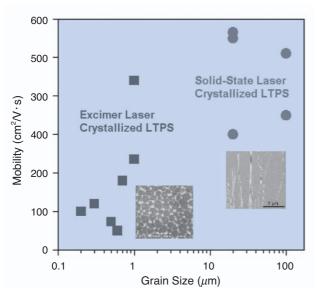

動率是必需的,但由於複晶矽的原罪使得薄膜電晶體容易受到複晶矽晶界的數量與位置影響而造成特性漂移與不均匀,為了不讓複晶矽的晶界成為載子移動的障礙,下一代低溫複晶矽成膜技術成為開發的重點,如連續矽晶界、循序性側向結晶(sequential lateral solidification, SLS)、連續波雷射橫向結晶(CW-laser lateral crystallization, CLC)及選擇性擴大雷射結晶(selectively enlarging laser x'tallization, SELAX)製程等(如表 3 所示),皆可大幅提升低溫複晶矽薄膜電晶體的載子移動率。圖 6 為準分子雷射與固體雷射之比較,可以發現固體雷射技術可以達到接近單晶的薄膜。

為了增大晶粒尺寸,必須控制好成核時超級冷卻 (super-cooling) 的特性,較低的超級冷卻擁有較慢的結晶速率,配合外在的輔助工具 (如光罩)、内在的電晶體結構或薄膜圖形 (如表 3 所示),產生較大的溫度梯度,使得晶粒往同一方向成長,可以形成較大的晶粒尺寸。由於準分子雷射的熔融時間 (melting time) 約數十奈秒,形成極快的結晶速率,導致較小的晶粒尺寸 (約 0.1-1.5  $\mu$ m),而固態與

氣體雷射的熔融時間較長,有著較慢的結晶速率,因此晶粒尺寸也相對較大 (約 1-100 μm)。再加上固體或氣體雷射的成本較準分子雷射低廉,使得不少低溫複晶矽製造商積極的朝向這方面開發研究。Hitachi 利用準分子雷射搭配選擇性的 Nd:YVO₄ 雷射照射可達到 460 cm²/V·S 的移動率。而 Fujitsu 採用連續波的 Nd:YVO₄ 雷射所形成的高移動率 (566 cm²/V·S) 低溫複晶矽薄膜電晶體外,更將完整的 SRAM 記憶體整合於玻璃基板上。值得注意的是,當面板面積大於三十吋後,其製程難度大增,所需的投資成本相當大,不亞於傳統半導體製程,良率不易提升,將是未來開發的重點。

#### 五、閘極氧化層技術

為了達到低溫製程、大面積與高均匀度的目的,傳統的低壓化學氣相沈積與大氣壓化學氣相沈積與大氣壓化學氣相沈積並不適用於 TFT-LCD 的製造流程,而電漿輔助化學氣相沈積藉由電漿的輔助,同時可以達到低溫與大面積的優點,特別是第六代基板均匀度要求更是極大的挑戰,無論是底層 (buffer layer) 的  $SiO_2$  或  $SiN_x$ 、閘極氧化層或保護層都可見到其蹤影,是 LCD 面板製造不可或缺的武器。常見的閘極氧化層可藉由  $SiH_4/N_2O$  或 TEOS (tetraethy-orthosilicate)/ $O_2$  來成長,其中以 TEOS 所成長出來的閘

圖 6. 準分子雷射與固體雷射之比較。

極氧化層品質與覆蓋度 (step-coverage) 較佳,其均 匀性可達 4 至 5%。

然而傳統電漿輔助化學氣相沈積閘極氧化層時常需要高於三百度的溫度以確保薄膜品質,低溫所成長的閘極氧化層通常具有較多的缺陷與界面陷阱,可藉由沈積後高溫、高壓水蒸汽、雷射或快速熱退火輔助的動作,使得閘極氧化層中的缺陷減少並增加致密性,提高崩潰電壓以提升元件特性。另一種高效能成長閘極氧化層的方法為高密度電漿源的化學氣相沈積法,如感應線圈電漿(inductivelycoupled plasma, ICP)或電子磁旋共振電漿(electron cyclotron resonance, ECR),利用這類高密度電漿源所提供的低能量高游離載子密度的環境,使得電漿所造成的傷害降至最低(如表 4 所示)。而為了增加閘極氧化層的品質,利用 ECR-CVD 混合電漿輔助化學氣相沈積形成閘極氧化層,其崩潰電場都有不錯的表現。

另一方面,為了在低溫的環境下沈積氧化層,採取引控式電漿 (remote plasma, RP) 化學氣相沈積或光輔助式氧化層的概念,可以應用於塑膠基板的製程,利用電漿環境分離的方式,或在 excimer lamp 下將氧游離並反應生成光氧化層,其反應溫度在 25-350°C 之間 (如表 4 所示)。以這種無電漿環境沈積方式形成閘極氧化層,降低了薄膜表面被高能量離子撞擊 (ion bombardment) 所造成的界面缺陷與表面損傷,除了具有較佳的界面之外,元件特性有也不錯的表現,若能配合使用電漿輔助化學氣相沈積方式形成堆疊式 (stacked) 氧化層,可達事半功倍的效果。

由於塑膠基板的應用加上製程溫度的考量,以物理氣相沈積方式濺鍍或蒸鍍介電層也是未來的趨勢。再者為了達到更高的系統驅動能力與電容儲存容量,降低閘極氧化層的厚度成為勢在必行的趨勢。Toshiba 已成功地將 80 nm 閘極氧化層技術導入量產產品中,而高介電常數材質選用也是未來開發的重點之一,然而隨著氧化層厚度的變薄與新材質的應用,伴隨而來相關可靠度問題卻是不容忽視的。另外,對於氧化層的潔淨 (cleaning) 也是重點技術之一,由於目前低溫複晶矽多為上閘極結構 (top gate),不似下閘極結構具有連續沈積薄膜的優

表 4. 閘極氧化層的技術分類。

| 成膜方式            | 界電層材質                   | 厚度 (nm)  | 成膜溫度 (℃) | 崩潰電場 (MV/cm) | 參考資料                  |

|-----------------|-------------------------|----------|----------|--------------|-----------------------|

| PECVD           | TEOS-based              | 100      | 315      | 8            | M. Watatani, AMLCD 94 |

| PECVD           | SiH <sub>4</sub> -based | 350      | 280      | _            | KH. Lee, ED 98        |

| PECVD           | $SiN_x$                 | 350      | 280      | _            | KH. Lee, ED 98        |

| RPCVD           | SiH <sub>4</sub> -based | 100      | 350      | _            | K. Yuda, AMLCD 97     |

| ICP             | SiO <sub>2</sub>        | 10       | 350      | 9.3          | CH. Tseng, EDL 02     |

| ECR             | SiH <sub>4</sub> -based | _        | 80       | 5            | R. Rashid, MRS 01     |

| ECR + PECVD     | SiO <sub>2</sub>        | 20 + 80  | 100      | 3.5          | YJ. Tung, SID 98      |

| Photo + PECVD   | TEOS-based              | 4.3 + 40 | 300      | 8            | Y. Nakata, IDW 01     |

| Ion Plating     | SiO <sub>2</sub>        | 50       | 23       | 9.3          | CF. Yeh, EDL 96       |

| E-gun Evaporate | SiO <sub>2</sub>        | 100      | 100      | _            | CH. Kim, MRS 01       |

| Sputtering      | SiO <sub>2</sub>        | 20       | 200      | 10           | N. Yamauchi, ED 94    |

點,其界面常累積自生氧化層、有機物、微粒子與金屬雜質等,這類的不速之客易造成薄膜電晶體的特性漂移與劣化,因此氧化層與複晶矽之間的界面潔淨成為特性優劣的開發重點。常見的潔淨方式有DHF、紫外線臭氧、超音波震盪與化學清洗法等,而新一代的潔淨技術,如 RPSC (remote plasma source cleaning) 因具有更高效率而備受矚目。

# 六、平坦化與低阻值導線製程

為了達到大面積高解析度的面板,除了朝向新 一代大面積基板或無接縫技術 (seamless tiled) 的開 發外,降低面板訊號的延遲成為首要之務,藉由低 阻值導線與低介電常數材料的平坦化製程成為勢在 必行的趨勢。鋁合金是常見的低阻值材質,在 TFT-LCD 中已廣泛的用在導線上,但是鋁金屬薄 膜經過熱循環後,仍然存在著電子遷移 (electromigration)、應力空孔 (voids) 與堆積 (hillock) 等問 題,如果使用在資料線或掃描線路上可能會有短路 的情況發生,這在液晶顯示器的使用上是一個相當 大的問題,這類的問題可藉由陽極氧化、多層結構 或添加適當的高熔點金屬 (如 Al-Nd) 來改善,對於 應用於大尺寸 LCD 的內金屬導線是相當有幫助 的。而比起過去使用的鋁導線,銅或銀導線具有更 低的阻值 (如表 5 所示),有較佳的電阻-電容 (RC) 時間延遲及電子遷移特性,尤其當線寬愈來 愈窄的時候,其對高頻的影響愈來愈大,已被視為下一代高解析與大面積面板的明星製程(如圖7所示)。銅製程可採用銅濺鍍或電化學電鍍(electrochemical plating, ECP)的方式將銅鍍在玻璃上,且銅靶材比鋁靶材節省約六成左右的材料成本,加上銅或銀導線的抗電致遷移能力亦比鋁好,可減少導線斷開的機率,提高整合電路的可靠性。

由於銅或銀對於玻璃的附著性 (adhesion) 差,同時也為了避免銅或銀導線與矽產生反應並防止金屬離子擴散,常以一阻障層 (如 Ta, TiN, Al<sub>2</sub>O<sub>3</sub>, ITO..) 使其增加對玻璃或其他介電層的附著性,或採用一保護層 (如 Ta, AlN, MgO, Cr<sub>2</sub>O<sub>3</sub>…),以防止因環境或後續製程對於銅或銀導線所造成的傷害 (如表 5 所示)。除了降低導線阻值外,低介電常數之平坦化材料也亟待開發。低溫複晶矽內建高密度驅動電路與高解析度的畫素陣列,對於後段之平整性要求甚高。

傳統化學氣相沈積方式易造成覆蓋性不佳而形成導線間的短路,導致面板缺陷、液晶排列或有機發光材質的效率不佳。高透光度與低介電常數之平坦化材料將使 ITO 膜能藉此材料而跨在薄膜電晶體陣列基板上,擁有比傳統式 TFT-LCD 更大區域的 ITO 電極、更高的開口率,並提供平坦之表面,以利後續整合式彩色濾光片 (integrated color filters)、整合式黑色矩陣 (integrated black matrix)或整合式間隔體 (integrated spacer)、液晶或有機發光

圖7.解析度與面板尺寸對於導線材質之要求。

二極體製程<sup>(2)</sup>。可藉由塗布或化學氣相沈積方式形成低介電常數材料或感光材料 (如 benzocylobutene, BCB),可以有效的降低寄生電容、減少水氣及增加畫面品質,以延長面板的壽命。LG-Philips 已成功開發出 20.1 吋 UXGA 與 15 吋 QUXGA 之銅導

線非晶矽液晶面板,以高解析度與高積集性著稱的 低溫複晶矽,採用平坦化與更低阻值導線製程成為 不得不的趨勢。

# 七、結合可撓曲的塑膠基板製程

因應未來系統面板的需求並讓使用者隨意曲摺且隨身攜帶,利用低溫複晶矽薄膜電晶體較佳的特性與整合電路的優點,是搭配可撓曲面板(plastic/flexible display)的不二選擇(如圖8顯示)。目前塑膠基板顯示器開發的重點為可撓曲製程開發與顯示材料的選擇(如表6顯示)。而可撓曲製程開發主要分成兩大類,一類為將電晶體直接製造於塑膠基板的技術,另一類為塑膠基板轉移的技術。直接製作於塑膠基板與傳統薄膜電晶體的製程相容性高,但由於低溫複晶矽製程溫度約四百至五百度之間,在製造過程中會造成塑膠基板的形變與對準誤差,再加上塑膠基板的耐溫、耐溼與耐化學性不佳,使得製程上的困難度提高不少。除了採用更高穩定性的塑膠基板外,藉由開發直接濺鍍非晶矽、單晶矽與界電層,並配合雷射做結晶與活化的流

表 5. 低阻值導線製程分類。

| 導線材質 | 結構                                                    | 厚度<br>(nm) | 製程溫度<br>(°C) | 阻值<br>(μΩ-cm) | 參考資料                       |  |

|------|-------------------------------------------------------|------------|--------------|---------------|----------------------------|--|

| MoW  | MoW                                                   | 300        | _            | 13            | Toshiba                    |  |

| Mo   | Mo/Ta                                                 | _          | _            | 15            | _                          |  |

|      | Al <sub>2</sub> O <sub>3</sub> /Al                    | _          | _            | 3.5           | JH. Kim, SID 97            |  |

| Al   | Al-Nd                                                 | _          | _            | 5             | H. Kinoshita, SID 99       |  |

|      | TiN/Al/Ti                                             | _          | _            | _             | Sharp                      |  |

| Ag - | AlN/APC (Ag-Pd-Cu)<br>/Al <sub>2</sub> O <sub>3</sub> | 20/100/6   | 300          | 3.4           | SW. Lee, SID 02            |  |

|      | Ag                                                    | 100        | 300          | 2.1           | W. H. Lee, J.KPS 02        |  |

|      | MgO/Ag-Mg                                             | 100        | 300          | 4.2           | W. H. Lee, J.KPS 02        |  |

|      | Ta/Cu/Ta                                              | 50/200/50  | _            | 3.3           | M. Ikeda. Japan Display 89 |  |

|      | TiN/Cu/TiN                                            | 20//20     | 200          | 2             | S. He, IITC 98             |  |

| Cu   | AlN/Cu/ Al <sub>2</sub> O <sub>3</sub>                | 20/100/6   | 200          | 2.5           | SW. Lee, EDL 02            |  |

|      | Cu                                                    | 240        | _            | 2.5           | JH. Lan, EDL 99            |  |

|      | Cu/ITO                                                | _          | _            | 2             | P. M. Fryer, SID 96        |  |

|      | MgO/Cu-Mg                                             | 15/400     | 500          | 3.6           | W. H. Lee, APL 01          |  |

|      | Cr <sub>2</sub> O <sub>3</sub> /Cu-Cr                 | 20/160     | 400          | 4.5           | H. Sirringhaus, EDL 97     |  |

表 6. 低溫複晶矽薄膜電晶體應用一覽表。

| 面板種類                         | 基板材質                  | 尺寸(吋) | 解析度       | 特點                                                                                                                                                                                             | 參考資料                             |

|------------------------------|-----------------------|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Electrophoretic              | Glass                 | 3     | 320 × 240 | <ul> <li>Gray Scale = 4 Level</li> <li>Area Ratio Gray Scale</li> <li>Aperture Ratio = 75%</li> <li>EP Driven at 18 V</li> </ul>                                                               | S. Inoue, IEDM 00                |

| Organic Light Emitting Diode | Glass                 | 13    | 800 × 600 | <ul><li>Top-emission</li><li>4-TFT Current Mirror</li><li>Programming</li><li>Micro-Cavity Structure</li></ul>                                                                                 | T. Sasaoka, SID 01               |

| Light Emitting<br>Polymer    | Glass                 | 2.1   | 200×150   | <ul><li> Bottom-Emission</li><li> Area Ratio Gray Scale</li><li> Time Ratio Gray Scale</li><li> LEP Driven at 3 V</li></ul>                                                                    | T. Shimoda, IEDM 99              |

| Light Emitting<br>Polymer    | Plastic               | 2.1   | 200×150   | <ul> <li>SUFTLA Process</li> <li>Panel Thickness = 0.5 mm</li> <li>Panel Weight = 3.2 g</li> <li>LEP Driven at 3 V</li> </ul>                                                                  | S. Utsunomiya,<br>EURODISPLAY 02 |

| Liquid Crystal               | Glass                 | 3.82  | 480 × 320 | <ul> <li>6-Bit Data Driver and Scan         Driver Integrated     </li> <li>Interface Circuit Integrated         (Timing Generator, Reference         Driver, DC-DC Converter)     </li> </ul> | T. Maekawa,<br>EURODISPLAY 02    |

| Liquid Crystal               | Plastic<br>+<br>Glass | 8.4   | 800 × 600 | <ul> <li>Thin Glass and Attaching Flexible Sheet (0.4 mm)</li> <li>Normal LTPS Process</li> <li>Panel Weight = 20 g</li> <li>Radius of Curvature = 20 cm</li> </ul>                            | Toshiba                          |

| Liquid Crystal               | Plastic               | 0.7   | 428 × 238 | • SUFTLA Process • Frequency of Data Driver = 1.3 MHz • Frequency of Scan Driver = 4 KHz                                                                                                       | S. Utsunomiya, SID 00            |

| Liquid Crystal               | Plastic               | 1.5   | 240×160   | <ul> <li>Back-Etching Glass and<br/>Transfer to Plastic Substrate</li> <li>Normal LTPS Process</li> <li>Color Filter on Array</li> <li>Panel Weight = 0.5 g</li> </ul>                         | A. Asano, SID 02                 |

程,可有效的將製程溫度降低至一百五十度以下, 但由於設備機台較特殊,面板製造門檻較高。第二 類為塑膠基板貼合的技術,利用傳統已完成於玻璃 基板上的薄膜電晶體陣列與電路,以黏貼塑膠基板 的方式形成可撓曲面板,製程簡單且相容於目前面 板技術。或是採取雷射分離製程 (surface free technology by laser ablation/annealing, SUFTLA),其 將形成於玻璃基板的低溫複晶矽薄膜電晶體分離至 塑膠基板的技術,也相容於目前傳統的薄膜電晶體 製程,作為塑膠基板技術的跨入門檻較低,也頗受 市場關注,近來 Seiko Epson 成功地利用此技術發 表 AMLCD 與 AMLEP 的塑膠面板 (如表 6 所示)。 另外,可撓曲顯示材料的選擇五花八門,有高分子分散液晶 (polymer dispersed liquid crystal, PDLC)、有機發光二極體 (organic light emitting diode, OLED)、電子墨水 (E ink) 或 gyricon 這類含有微粒子的微囊體或帶色小珠材料,其中以有機發光二極體最為熱門。有機發光二極體具有反應速度快、重量輕、可撓曲與廣視角等優點,容易與低溫複晶矽薄膜電晶體結合,且由於非晶矽薄膜電晶體的載子遷移率與驅動電流較小 (約 0.1 μA),欲驅動高亮度有機發光二極體需要較高的電壓與較大的元件,而低溫複晶矽的高電流特性 (約 15 μA) 正好符合有機發光二極體嚴苛的要求,低操作電壓與高密度的驅動架構使得有機發光二極體壽命延長。

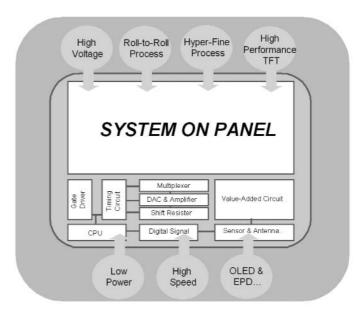

為了驅動有機發光二極體,需要特殊電流驅動架構,並克服灰階與面板均匀性所設計的補償電路,在同一畫素中需要二至六個薄膜電晶體,加上傳統的有機發光二極體畫素大多為下部發光結構,往往薄膜電晶體與資料導線成為阻礙光線通過的瓶頸。以低溫複晶矽較小設計準則與高密度布局的特點,使得有機發光二極體的發光區域增加並延長壽命,使得高亮度與高畫質的面板更容易實現。另外由於各家面板廠商所採用的規格與驅動架構均不相同,低溫複晶矽整合電路的優點提供了客戶導向設計的好處。對於效能與速度不斷提升、訴求多功能性的低溫複晶矽面板而言,未來若能搭配大量捲帶式連續生產製程技術 (R2R, roll-to-roll process) 的開發,相信將會更具優勢與競爭力 (如圖 8 顯示)。

#### 八、結語

因應大面積與高解析度的趨勢,除了積極提升 低溫複晶矽的技術外,還需配合周邊的相關技術, 如整合式彩色濾光片、有機發光二極體與可撓曲基 板製程,達到相輔相成的功效。平面顯示器的趨勢

圖 8.系統面板 (system on panel) 的需求。

將會帶來更多整合的周邊電路與附加價值,相對的 也需要更佳的低溫複晶矽特性。面對未來新一代基 板的挑戰與日韓面板廠的相互競爭,如何開發新製 程與應用市場將是台灣邁入國際舞台的重要一環, 也是值得學術界與產業界共同研究與開發的重點!

#### 參考文獻

- 1. N.-H. Kung et. al., SID, 908 (2002).

- 2. 莊景桑等,電子與材料雜誌,14期,113.

陳志強先生為國立清華大學工程與系統科學研究所碩 士,現任工業技術研究院電子工業研究所工程師。

Chih-Chiang Chen received his M.S. in engineering and system science from National Tsing Hua University. He is currently an integration engineer of Electronics Research and Service Organization at Industrial Technology Research Institute.