磁性材料及元件應用技術-磁阻記憶體近期發展與挑戰

Magnetic Materials & Related Technological Applications-Recent Development and Challenge of Magneto-resistive Random Access Memory

隨半導體產業日新月異,電晶體微縮進展日新月異;即使逼近物理極限,各大研究團隊仍孜孜矻矻探究各種可能性。然而記憶體在微縮上卻難以望其項背,因此新興記憶體的需求也相應而生,磁阻式記憶體即為其中之一。磁阻式記憶體有著非揮發性的特質,且讀寫速度快,可覆寫次數高,使其成為極具潛力的候選者,然而其製程上卻有相當程度的挑戰,本文將從自旋轉移力 (spin-transfer torque, STT) 矩式記憶體出發,延伸到近期非常熱門的自旋軌道轉移矩 (spin-orbit torque, SOT),探討相關技術的發展與瓶頸。

With the rapid development of the semiconductor industry, the progress of transistor miniaturization is made rapidly. Even though the physical limits are approaching, major research teams are still diligently exploring various possibilities. However, memory technology is not as good at miniaturization as it should be, so there is a demand for new memory, one of which is magneto-resistive random access memory (MRAM). MRAM has non-volatile properties, with fast read/write speed, and high overwriting frequency. These merits make it a promising candidate for next-generation memory technology. However, there are considerable challenges in MRAM in terms of the fabrication process. In this report, we explore the development and bottlenecks of this technology, first from the perspective of spin-transfer torque (STT) MRAM. We then extend to the spin-orbit torque (SOT) MRAM, which is a very popular research topic of the technology.

一、前言

磁阻式記憶體發展行之有年,早期透過電流磁效應產生磁場,進而使磁性層反轉,藉此改寫儲存位元態,然此種方式需要相當高的寫入電流,且於電路中產生磁場對其他電子元件造成干擾。爾後由於自旋轉移力矩的發現,當非極化電流穿過鐵磁性材料衍生出極化電流,由於極化電流本身帶有自旋電子數量不平衡,根據角動量守恆 (Conservation of Angular Momentum),藉此自旋電流誘使鐵磁層磁矩翻轉,覆寫原先儲存位元,此種寫入機制改善了早期需要實際產生磁場的缺點,可透過電訊號來改寫記憶體儲存位元,使磁阻式記憶體與半導體製程相容性更高,即所謂自旋轉移力矩式 (spin-transfer torque, STT) 磁阻記憶體 (magneto-resistive random access memory, MRAM),歷經長時間的研究發展,已慢慢步入商業化,根據 Research and Market 預估,MRAM 產業市場規模將於 2026 年到達近 50 億美元(1),且各大廠牌與研究團隊仍致力於推展商業化與研發腳步,希望取代 DRAM 等傳統記憶體,此外應用於嵌入式記憶體也是一大商機。STT-MRAM 的誕生,替記憶體產業帶來新的可能,然而其製備卻有相當程度的挑戰性。從鍍膜製程角度來說,由於 MRAM 讀取機制源自於量子穿隧效應,因此氧化層厚度必須薄到可供電子穿隧 (約一奈米),要製備均勻連續的氧化薄膜本身就具有挑戰性;另外若須達到足夠高的穿隧磁阻 (tunneling magnetoresistance, TMR),氧化層需要良好且正確的結晶性,因此退火條件的選擇也是重要考量,其中又牽涉到各膜層間擴散效應,因此適當的阻擋層搭配也是重點;最後磁性層的生長更是至關重要,如何透過製程調整磁異向性也會大幅影響 MRAM 表現,不論是透過形狀異向性 (shape magnetic anisotropy) 或是材料本身的磁晶異向性 (magneto-crystalline anisotropy),甚至是透過膜層設計釘札層 (pinned layer),藉由交換耦合能 (exchange coupling) 綁定磁矩排列方向都是常見的方式,也因此單單是第一道鍍膜製程就令人敬而遠之。即便克服了鍍膜製程,黃光微影製程是否能製備足夠小的磁穿隧結 (magnetic tunnel junction, MTJ) 也是重點項目,倘若 MTJ 尺寸過大,電流密度則不足以翻動磁矩,令許多不具備良好微影技術的團隊難以推進;此外 MTJ 由於磁特性對尺寸效應相當敏感,MTJ 在大尺寸呈現多磁疇分布,而在尺寸逐漸縮小後轉為單磁疇分布,因此其翻轉機制上會有相當大的差別,導致團隊在開發不同尺寸的 MTJ 上經驗難以複製。最後在蝕刻製程上更是舉步維艱,蝕刻終點若是無法準確控制,則會對磁性層造成損傷影響元件特性,而蝕刻的副產物回濺則會導致 MTJ 短路問題發生。綜上所述,MRAM 由於製程上難度相當高,但所幸歷經長久以來世界各研究團隊的協心戮力,才有了今日邁入商業化的契機,本文先介紹磁阻式隨機記憶體發展,討論製程遇到的瓶頸,與相關的量測分析與模擬方式。

二、自旋轉移力矩式磁阻記憶體發展

磁阻式記憶體的發展源遠流長,集大成於一家,本節從記憶體的三大主要功能介紹:讀取、覆寫與儲存,藉此快速介紹 STT-MRAM 的基本功能。

1. 讀取

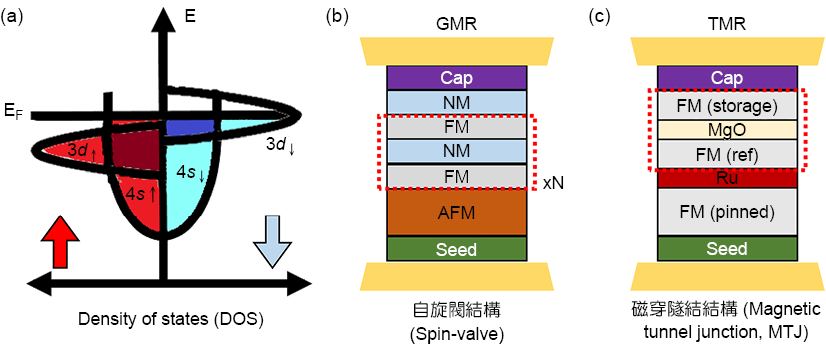

磁阻式隨機記憶體讀取機制可追溯至巨磁阻效應 (giant magnetoresistance ratio, GMR) 談起,主要機制是由於鐵磁性材料含有不成對 d 軌域電子,導致本身自旋向上與自旋向下電子數目不一致,如示意圖 1(a),當非極化電流通過時,會造成自旋相依散射 (spin-dependent scattering),造成不同方向自旋電子於路徑中移動時產生不同程度的散射,進而產生電阻差異;而穿隧磁阻效應則與巨磁阻相似,整合量子穿隧效應 (tunneling effect),透過改變夾層為超薄氧化層,進一步對自旋電子進行篩選,以達到更高的穿隧磁阻效應 (tunneling magnetoresistance ratio, TMR),因此現今 MRAM 讀取機制主要仰賴 TMR。兩者結構如示意圖 1(b),分別為常見的自旋閥結構 (spin-valve) 與磁性穿隧結結構 (MTJ),自旋閥結構於 1991 年由 B. Dieny 提出(2),結合巨磁阻的鐵磁層-非磁層-鐵磁層三明治結構堆疊,並結合反鐵材料加強單層鐵磁層異向性;而磁性穿隧結結構則是將三明治結構替換成鐵磁層 (自由層) -氧化層-鐵磁層 (釘札層),並透過人工反鐵磁層 (synthetic antiferromagnetic, SAF) 強化鐵磁層異向性,最早的實驗由 J.S. Moodera(3) 與 T. Miyazaki(4) 等人於 1995 年成功製備出於室溫具備穿隧磁阻效應元件。

圖 1. (a) 鐵磁性材料由於內部電子排列,使其於 3d 軌域具有孤對電子,造成淨自旋不為零。(b) 自旋閥結構,主要使用巨磁阻效應。(c) 磁穿隧結結構,主要使用穿隧磁阻效應 (資料來源:本研究團隊)。

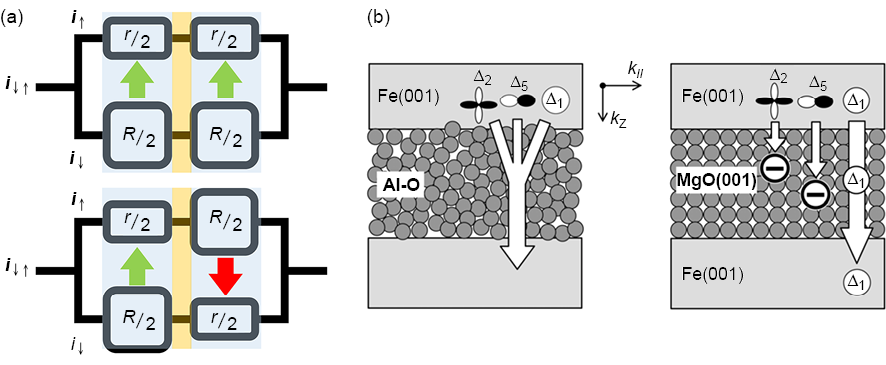

巨磁阻效應可進一步由雙通道電流模型來解釋,如示意圖 2(a),當鐵磁層平行排列時,可得到等效電阻為 Reff = Rr/(R + r);當鐵磁層反平行排列時,可得到等效電阻 Reff = (R + r)/4。而穿隧磁阻模型,主要根據是否考量電子波函數對穿隧機率的程度差異分為 Julliere 模型(5) 與 Slonczewski 模型(6),如示意圖 2(b)。在 Julliere 模型中,不考量電子本身差異,在早期非結晶氧化層如氧化鋁仍可描述,透過非同調穿隧 (incoherent tunneling) 進行,後來第一原理計算發現,穿隧機率與軌域對稱性有高關聯性,因此改選用 MgO (001) 作為氧化層,由於自旋篩選效應 (spin-filtering effect),特定布洛赫波 (Bloch state) 能夠更有效率的傳遞,因此穿隧磁阻率有大幅度的提升,實驗也轉為 Slonczewski 模型描述,考量了電子波函數的不同,更貼切的描述了現有磁穿隧結的狀態。在 2008 年由 S. Ikeda(7) 等人發表的磁性穿隧結即可於室溫下達到 604% 的高磁阻率,至此 MRAM 之核心已逐步成形。其他磁阻效應還包含異向性磁阻 (anisotropy magnetoresistance, AMR)、自旋霍爾磁阻 (spin Hall magnetoresistance, SMR) 等等,藉由鐵磁層磁矩排列與操縱電流方向,可以更深入得知背後的物理機制,以及推廣到更廣的應用範疇,如感測器等等。

圖 2. (a) 雙電流等效電路模型,描述不同鐵磁層排列下電阻變化。(b) 非結晶氧化層與結晶氧化層差異,考量電子波函數於結晶氧化層中穿隧機率差異(8)。

2. 覆寫

MRAM 寫入機制早期為磁場翻轉 (Toggle MRAM),然則其能耗極高,且由於寫入機制透過磁場產生,為了避免不同位元寫入干擾,因此在微縮方面有很大的限制,所幸自旋轉移力矩的發現,催化了 STT-MRAM 的誕生,可透過電流直接操縱磁矩方向。

自旋轉移力矩理論早於 1996 年由 Slonckewski(9) 與 Berger(10) 提出,1998 年由 M. Tsoi(11) 等人用實驗證實自旋轉移力矩之存在,2000 年由 J.A. Katine 等人於自旋閥 (spin-valve) 結合了自旋轉移力矩(12),最後於 2004 年才有團隊成功製作出結合自旋轉移力矩之磁性穿隧結(13)。當電子由釘札層往自由層流動,

由於鐵磁性材料含有不成對的 3d 軌域電子,使非極化電流轉而形成極化電流,並根據釘札層磁矩方向帶有特定自旋角動量,當此自旋電流穿越過非磁性材料抵達自由層與非磁性層之介面,由於角動量守恆,自旋電流即被自由層吸收,因此使自由層翻轉與釘札層平行方向,即為自旋轉移力矩原理,如圖 3(a);當電子流由自由層往釘札層移動,自旋電子抵達釘札層與非磁性層介面,與釘札層反向之自旋電子無法穿透因而背向散射回自由層,導致自由層翻轉與釘札層反平行排列,如圖 3(b)。

圖 3. 釘扎層與自由層 (a) 從反平行排列翻轉至平行排列;(b) 平行排列翻轉至反平行排列 (資料來源:本研究團隊)。

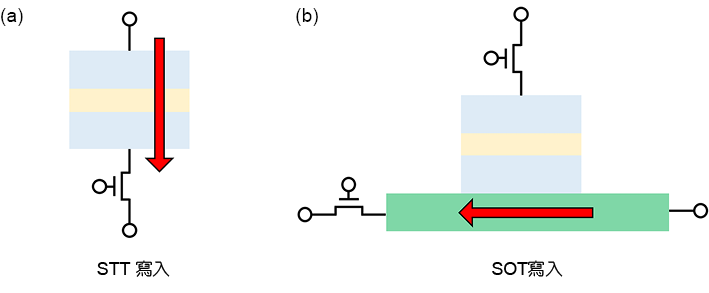

由於自旋轉移力矩的開發,克服了磁場翻轉無法微縮的缺陷,使 STT-MRAM 成為 DRAM 面臨微縮瓶頸的替代方案,然而其仍有潛在的缺陷,即是翻轉電流仍然相當高,翻轉電流密度數量級約為 MA/cm2,而磁性穿隧結本身為超薄的氧化層,因此氧化層崩潰等可靠度問題也是一大隱憂,因此如何降低翻轉電流密度與增加氧化層可靠度即是研究重點項目。而近幾年隨著研究發展,自旋軌道轉移矩 (spin-orbit torque, SOT) 的發現(14),提供了 MRAM 全新的寫入機制,藉由重金屬材料本身擁有很強的自旋-軌道耦合 (spin-orbit coupling, SOC) 當電子經過後針對不同自旋方向之電子,產生不同方向之偏移,因此產生的帶有特定方向的自旋電流,便如同自旋轉移力矩透過鐵磁層產生極化電流,為極化電流產生多了一項操縱手段,此種設計需要於自由層底部設計具有強自旋-軌道耦合作用材料,因此分離了讀寫路徑,連帶解決的 STT-MRAM 可靠度的問題,兩者操作差異如圖 4 所示,更有許多團隊投入於研究具有強自旋-軌道耦合效應之材料,如二維材料、拓樸材料等等。

圖 4. (a) STT (spin-transfer torque) (b) SOT (spin-orbit torque) MRAM 寫入示意圖 (資料來源:本研究團隊)。

3. 儲存 (scaling)

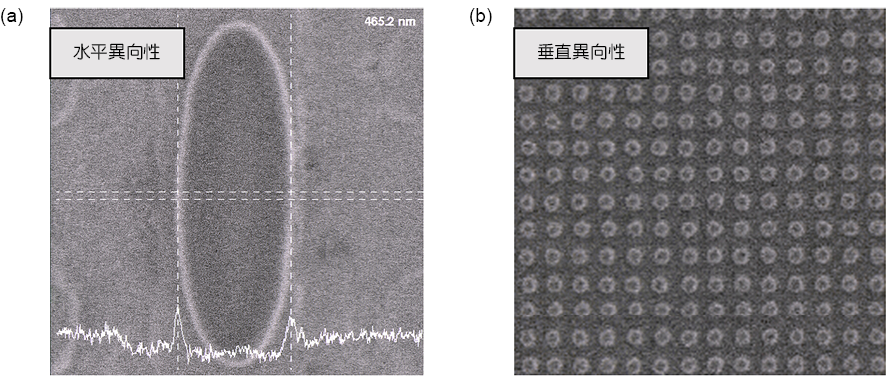

MRAM 儲存機制一般主要與自由層磁異向性相關,根據磁異向性又可分為水平式 (in-plane magnetic anisotropy, IMA) 與垂直式 (out-of-plane magnetic anisotropy, PMA)。其中判斷儲存能力的因子稱為熱穩定性 (thermal stability),公式定義如:D = (HkMsV)/(2kBT),Hk 為異向場 (anisotropy field),Ms 為飽和磁化強度 (saturation magnetization),V 為磁性層體積,kB 為波茲曼常數,T 為溫度,如果要使資料穩定保存十年,則熱穩定性必須大於 60。早期由於設計多為磁場翻轉,磁異向性皆屬平行膜面排列,然而其仰賴形狀異向性來強化磁矩方向,磁性穿隧結必須蝕刻成橢圓形,倘若長寬比 (aspect ratio) 小於 2,容易於邊緣產生渦旋態造成寫入錯誤,由於形狀的限制,平行膜面磁性穿隧結有其微縮的限制;此外,水平異向性薄膜本身異向場較弱,在持續微縮下將無法穩定保持足夠的熱穩定性,導致資料流失;幸運的是,垂直異向性的發展又給了 MRAM 新的未來,兩者差異如圖 5。從磁學來看,薄膜結構在 X 與 Y 方向之退磁場因子 (demagnetizing factor) 幾乎可忽略,但在 Z 方向約略等於 1,因此要使磁矩站立垂直於膜面是相當困難,而 S. Ikeda 等人克服了這項限制(15),將鐵磁層變薄,由於介面異向能 (interfacial anisotropy) 主導,使磁異軸轉為垂直膜面,而如此設計下的磁性穿隧結,不須倚賴形狀異向性,所以沒有了難以微縮的問題;另外也有了更強的磁異向場,使元件在微縮更小尺寸時不至於流失過多熱穩定性,也因此開啟了許多垂直異向性研究,透過各種介面效應來加強垂直異向性,例如透過 CoFeB 與 Ta 介面、CoFeB 與 MgO 介面(16),使原先簡單的自由層,逐步演變成 CoFeB/Ta/CoFeB 等複合式結構,當中針對重金屬層的置換、退火溫度的調整、元素擴散的探討更是琳瑯滿目。遺憾的是,在逐步微縮到 20 nm 以下後,依然面臨到了無法維持高熱穩定性的物理限制,而在 2018 年由 K. Watanabe 等人提出透過製程的手段(17),將磁穿隧結最小做到 4 nm,並且增厚鐵磁層,再一次利用形狀異向性的手法,使磁性穿隧結依然保持垂直異向性,又能透過更厚的鐵磁層維持熱穩定性,使 MRAM 在微縮的路上依然保持著相當程度的競爭力。

圖 5. (a) 水平磁異向性 (b) 垂直磁異向性磁性穿隧結 (MTJ) 掃描電子顯微鏡圖。由於後者不需仰賴形狀異向性,因此可進一步微縮。(資料來源:工研院電光所)

三、自旋轉移力矩式磁阻記憶體瓶頸

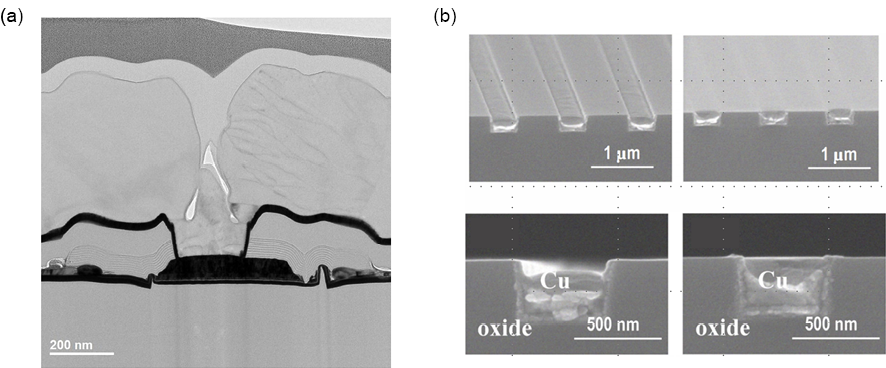

MRAM 透過長期以來的發展,讀取機制透過穿隧磁阻,寫入機制透過自旋電流,資料儲存上也有垂直異向性的輔助,然而在邁入量產的過程卻仍然有著瓶頸,就是製程上的複雜度,如何去監控也是亟須克服的問題,以下針對自旋轉移力矩式磁阻記憶體,在製程中可能面臨到的瓶頸加以討論。首先,鍍膜前必須確保表面平坦均勻,由於磁性穿隧結相當纖細複雜,極小的不平整都會影響到後續薄膜沉積,尤其是氧化鎂膜層品質,甚至影響到元件可靠度,降低崩潰電壓造成意外的短路,因此在薄膜沉積前先對基板做化學機械研磨 (chemical-mechanical polishing, CMP),透過機械性的研磨,配合適當的研磨漿液 (slurry),使基板表面平整化。以銅導線為例,容易產生元件失效的原因是材料研磨速度過快,產生碟型凹陷(Dishing),進而影響到薄膜沉積平整性,如圖 6(a) 所示,磁穿隧結成長於不平坦的銅導線上,進而影響元件特性,透過添加 Benzotriazole (BTA) 可改善此現象(18),如圖 6(b) 所示,另外也可透過移除部分表面金屬,重新回填適當的金屬材料再加以研磨,使基板平坦化;而研磨漿液本身帶有的研磨粒子若是殘留,也會使磁穿隧結失效。

圖 6. (a) CMP 產生碟型凹陷 (Dishing) 穿隧電子顯微鏡圖。(b) 加入 BTA 後,銅表面凹陷 (左圖) 改善,形貌更為平坦 (右圖)(19)。

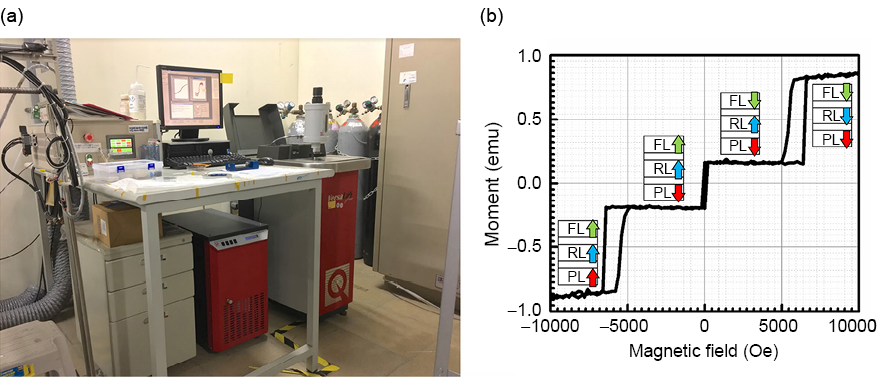

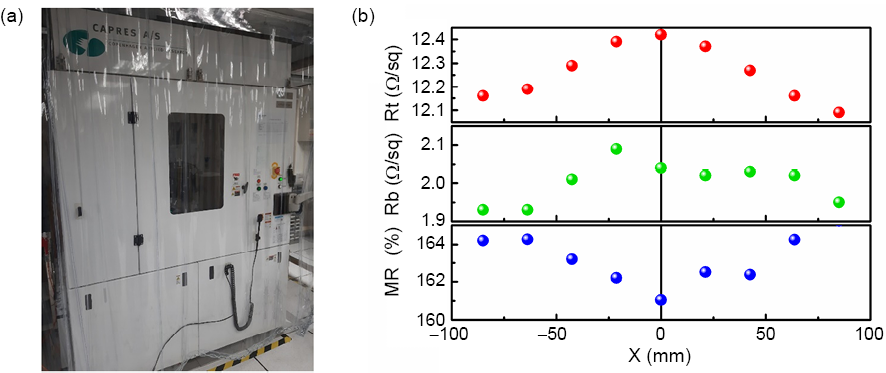

當基板平坦化後,再進行薄膜沉積與退火處理,磁穿隧結對於薄膜沉積的機台要求相當高,一般採用濺鍍 (sputtering) 製程,必須保持良好的均勻性,鍍膜速率必須緩慢到足以控制埃等級的薄膜厚度,且氧化物品質要求高,須以超高真空腔體進行沉積,以準確控制氧化物計量比及預防缺陷發生;而退火條件一般在攝氏 250 到 350 度,誘使膜層產生良好結晶,以達到更好的穿隧磁阻效應,透過膜層設計則可進一步提高退火溫度,抑制膜層中元素擴散傷害磁性層,以達到後道工序 (Back end of line, BEOL) 所要求的攝氏 400 度;此外,透過磁場退火工序,將溫度升高至反鐵材料的尼爾溫度 (Néel temperature) 與鐵磁材料的居禮溫度 (Curie temperature) 之間,打亂反鐵磁層磁矩,再透過外加磁場固定鐵磁層磁矩方向,當溫度下降後使反鐵磁層重新排列,藉此產生偏置場 (exchange bias),強化鐵磁層磁矩排列。當鍍膜完成後,一般會以振動樣品強磁計 (vibrating sample magnetometer) 檢驗磁滯曲線,附圖 7(a) 為實驗室機台圖,腔體內部含有一固定方向電磁鐵,可根據欲量測磁場為垂直或水平方向選用不同類型載台,磁場強度最高可達 3 T,溫度範圍可從 50 K 到 400 K,磁場解析度為 10-6 emu;當試片於腔體內振動,在不同磁場下有不同的磁化強度,透過感應線圈量測磁力線變化程度,轉換成感應電壓,即可測試材料磁矩 (magnetic moment),若進一步除上薄膜體積即可得到磁化強度 (magnetization),量測磁滯曲線如附圖 7(b),量測樣品為垂直式磁性穿隧結,主要結構包含自由層 (free layer, FL)、參考層 (reference layer, RL) 與固定層 (Pinned layer, PL),因此可以分析不同磁性層磁矩,確保樣品磁性符合正常,然實際薄膜結構產生的磁阻效應主要與氧化層品質有關,無法直接透過磁性分析來判斷,因此必須以電流平面穿隧量測 (current-in-plane tunneling, CIPT) 做監控,附圖 8(a) 為量測機台,其量測原理為透過十二根探針,藉由四點探針的量測方式,以不同針距量測片電阻,並且藉由穿隧層上膜層電阻 (Rt)、穿隧層下膜層電阻 (Rb) 做計算,藉此得到對應的 MR 與 RA 值 (resistance-area product),如附圖 8(b),透過 VSM 與 CIPT 的交叉量測,就能夠在薄膜階段分析膜層是否出問題,加快元件開發時間,而不用等到元件產出才得知結果。

圖 7. (a) 振動樣品強磁計 (VSM) 機台 (b) 磁滯曲線 (Hysteresis loop)。(資料來源:本研究團隊)

圖 8. (a) 電流平面穿隧量測 (CIPT) 機台 (b) 不同晶圓位置測試結果。(資料來源:工研院電光所)

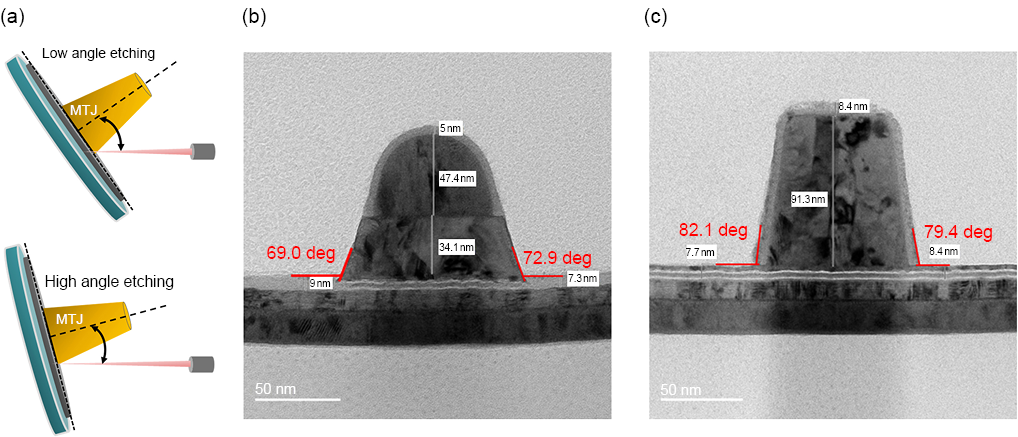

當薄膜沉積完成後,接著進行圖案化製程。在微影階段可透過深紫外光 (DUV) 或電子束直寫 (E-beam lithography),主要取決於磁穿隧結尺寸與機台的曝光能力,在電子束直寫必須選擇適當的曝光電子量 (dose),否則光阻形貌改變也會影響到後續磁穿隧結蝕刻,然而最關鍵的問題則是後續蝕刻的瓶頸。蝕刻製程一般可區分為乾式蝕刻 (dry etching) 與溼式蝕刻 (wet etching):濕式蝕刻透過化學溶液,侵蝕掉無光阻覆蓋區域,優點是成本低廉、高選擇比與速度快,然其蝕刻為等向性,在製作如磁穿隧結具有高深寬比的元件上容易造成底切 (undercut) 嚴重影響元件表現,因此無法做為主要蝕刻手段;而乾式蝕刻主要是透過電漿轟擊移除材料,可透過調整加速電壓等方式,為非等向性蝕刻,其中又可細分成化學性與物理性蝕刻。化學性最常使用於 MRAM 製程的為反應性離子蝕刻 (reactive ion etching, RIE),可針對不同蝕刻材料,通入不同蝕刻氣體來增加選擇比,一般半導體常用的 Cl2,在蝕刻磁性元素會造成表面粗糙並且影響磁性,因此必須尋找其他非腐蝕性的蝕刻氣體,例如 CO/NH3 與 MeOH 等等,但磁性金屬在蝕刻過程中容易產生非揮發性的金屬副產物,當副產物回鍍 (residue redeposition) 嚴重會使氧化層從側壁導通,造成磁穿隧結短路失效;而物理性蝕刻主要為離子束蝕刻 (ion beam etching, IBE),透過不同角度的離子束入射,可對磁穿隧結不同位置做修飾,減少 RIE 產生的回鍍物短路問題,然而其不利於高密度記憶體製備,當磁穿隧結密度過高時會造成陰影效應 (shadow effect) 而失去修飾效果,因此一般將結合 RIE 與 IBE,可以得益於 RIE 對高密度記憶體蝕刻的優勢,再配合 IBE 做適當的表面修飾,如圖 9(a) 所示,圖 9(b) 為形貌較為塌斜的磁穿隧結,圖 9(c) 則為形貌較為陡直的磁穿隧結,而在較為陡直的磁穿隧結可減少底部磁性層受損的概率,得到較好的磁特性。最後,需沉積絕緣層保護磁穿隧結,而由於磁穿隧結尺寸相當小,因此無法利用對位曝光連接上電極,必須利用回蝕刻 (etching back) 打開上電極連結,再回填電極材料,其製程也不容易準確控制蝕刻停止,若蝕刻深度不夠,元件會造成斷路而無法測試;倘若過度蝕刻,導致元件上下電極連通則造成短路,因此整個 MRAM 製程有許多造成失效的可能,在製程中可提供監控指標的量測手法也相當重要,例如採用磁光柯爾顯微鏡 (Kerr microscopy),透過極化光入射,由於磁性薄膜會與極化光交互作用,透過量測反射光的訊號可以得知元件磁特性,即為磁光柯爾效應 (magneto-optic Kerr effect, MOKE),此提供了在元件做最後導線連接以前,能夠測量圖案化後的元件磁性,由於蝕刻的製程變異極大,此手法能夠實際比較薄膜與元件的磁特性差異,藉此釐清磁性失效是否來自於蝕刻造成的損傷;而在導線連接以前,電性則可藉由導電式原子力顯微鏡 (conductive atomic force microscopy, C-AFM) 做分析,可在蝕刻完成後判斷元件電性是否符合預期。

圖 9. (a) 透過改變基板位置,調整 IBE 修飾角度,藉此清理不同位置殘留副產物。(b) 不同蝕刻條件,得到形貌較為塌斜的磁穿隧結。(c) 不同蝕刻條件,得到形貌較為垂直的磁穿隧結 (資料來源:工研院電光所)。

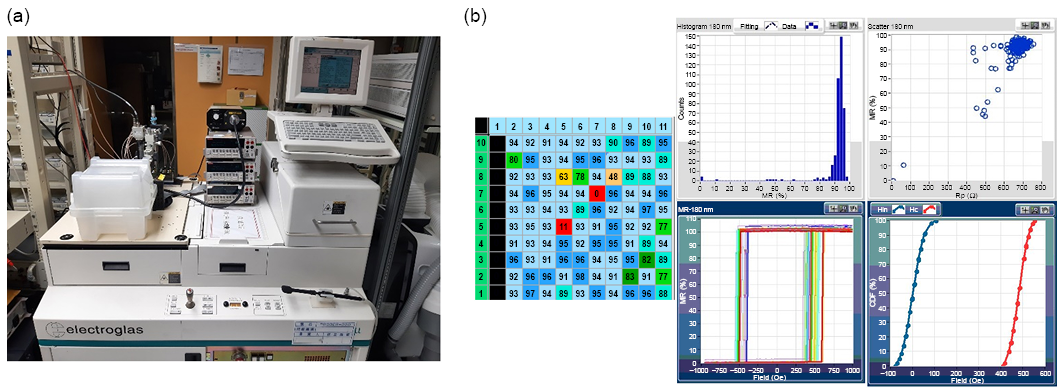

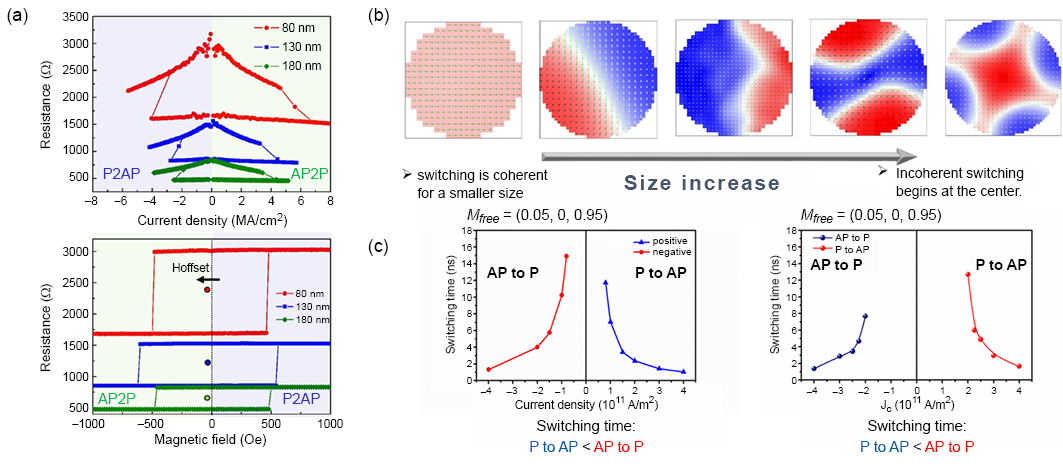

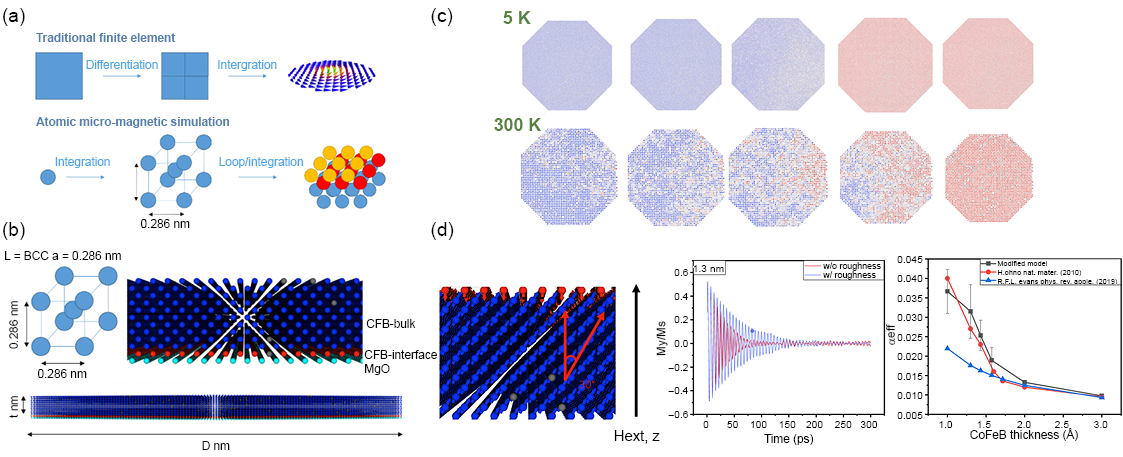

當磁穿隧結產出後,使用自動化晶圓量測設備進行參數分析 (wafer acceptance test, WAT),如圖 10(a),機台可自動化抓取晶舟內的晶圓作測試,晶圓置放於載台以真空吸附,透過機台自動對位系統定位晶圓上的對準標記 (alignment mark),自動旋轉晶圓到固定位置,並且利用噴嘴測試不同位置的膜層厚度,再將量測值回饋到系統內做修正,調整後續實際下針深度。圖 10(b) 為量測常見的可分析參數,例如低阻態電阻 (Rp)、電阻-磁場翻轉圖 (R-H loop),擷取出整片晶圓的磁阻值,可以觀察到是否有均勻的特性表現,初步判斷失效可能相關製程;而從磁阻值與電阻的散佈圖,能夠得知元件是否有側壁短路、寄生電阻等問題;從 R-H 曲線與累積分布函數,能夠得知元件在製程中是否有磁性上的損傷,針對晶圓做初步分析後,可再繼續進行快速翻轉測試、可靠度測試等等。圖 11(a) 為磁穿隧結分別透過電阻-電流密度翻轉圖 (R-J loop) 與電阻-磁場翻轉 (R-H loop) 實驗數據,可觀察到在尺寸微縮的情況下,翻轉電流密度逐步上升;另外可觀察到翻轉電流密度不對稱,從反平行態翻轉至平行態需要更高的翻轉電流密度,然而從 R-H 曲線來看,元件本身偏移場 (offset field) 非常小,因此翻轉不對稱可能不單純來自於離散場造成的影響,為了更進一步釐清磁穿隧結翻轉機制,本研究團隊同時也建立微磁模擬分析 (micromagnetic simulation),藉此分析元件可能狀況,透過微磁模擬可以觀察內部磁矩翻轉機制的差異,如圖 11(b),當磁穿隧結尺寸較大時,其翻轉由邊緣產生數個磁疇往中心移動;然而當磁穿隧結尺寸較小時,元件尺寸逐漸小於單個磁疇大小,其翻轉為整個元件透過單一磁疇同時翻轉,因此需要更高的電流密度才能達成翻轉。而圖 11(c) 中,透過給予自由層一個極小的傾斜角 (5 度) 可以發現,假如在自由層本身並未完全垂直於膜面的情況下,其反平行往平行態翻轉速度較慢,代表著其需要更高的電流密度進行翻轉,與實驗趨勢一致,因此可藉此推估元件在磁異向性可能垂直異向性不夠強,因此可再從製程重新調整。然而微磁模擬仍然有其限制,那就是面對非磁性物體時,本身並沒有太多的模擬參數可以代入,而實際上如反鐵材料等等,雖然由於自旋排列互相抵消而沒有磁性,但在介面仍可能存在單層不平衡的自旋排列,對接壤的鐵磁層產生偏置場 (exchange field),因此研究團隊也針對原子層級模擬 (Vampire) 做研究(19),其為約克大學開發的免費開源軟體,有別於一般的模擬方式,其從個別原子做單位,再以其做為堆疊基礎排列出不同元素的基本晶格 (圖 12(a)),因此其可代入原子晶格參數,也可透過建模調整介面的粗糙度 (圖 12(b))。實驗室透過原子層級模擬分析在不同溫度下的磁矩翻轉狀況,如圖 12(c),在低溫 (5 K) 條件下,整體翻轉為同調翻轉 (coherent switching),透過單一磁疇進行翻轉;在室溫 (300 K) 條件下,可以觀察到內部磁疇由於熱擾動的關係產生許多磁疇,造成非同調翻轉 (incoherent switching),因此在低溫下才需要更大的磁場才足以翻動磁矩。此外本團隊也藉由此模擬方式,分析自由層厚度模擬磁阻尼係數的變化,如圖 12(d),圖中自由層厚度-阻尼係數實驗數據 (標示紅色) 為擷取自 S.Ikeda 等人實驗數(15),在鐵磁層越來越薄時,阻尼係數快速上升;而從模擬數據 (標示藍色),S. Sampan-a-pai 模擬出自由層厚度與阻尼係數關係(20),在較厚的區域與實驗數值吻合,而在較薄的區域卻無法吻合實驗趨勢;因此本團隊進一步帶入粗糙度進入模型修正,由於自由層較薄時,介面粗糙度的影響相對更明顯,最後計算出的理論值更加貼近實驗結果,因此可佐證介面粗糙度在 MRAM 中造成了一定程度的影響,造成翻轉更加困難。

圖 10. (a) 晶圓自動化測試 (WAT) 機台。(b) 根據整片晶圓位置快速測試其良率分布位置圖、MR 分布直方圖、TMR 與 Rp 散佈圖、R-H 圖與矯頑場和偏置場累積分布函數 (資料來源:工研院電光所)。

圖 11. (a) 實驗量測不同尺寸磁穿隧結 R-J 與 R-H 作圖。(b) 透過微磁模擬觀察磁矩翻動模式 (模擬軟體:The Object Oriented MicroMagnetic Framework (OOMMF))。(c) 改變自由層初始傾角,模擬所需翻轉時間。P 與 AP 各自代表自由層與釘扎層磁矩處於平行 (低阻值) 態與反平行 (高阻值) 態 (資料來源:本研究團隊)。

圖 12. (a) Vampire 模擬分析概念圖。(b) Vampire 相關可帶入參數。(c) 改變不同環境溫度,模擬磁矩翻轉情形。(d) 利用 Vampire 建模,帶入粗糙度做計算,分析阻尼係數在不同介面粗糙度下的改變 (資料來源:本研究團隊)。

四、結論

MRAM 在長期的研究發展下具有極高的發展性,而 STT-MRAM 已邁入商業化逐步量產,當未來記憶體微縮遇到瓶頸,可做為替代品的候選者,然而在製程上還是有許多的瓶頸,也需要更多的量測手段來偵錯,在薄膜階段可以透過 VSM 分析磁性,配合 CIPT 量測電性如 MR 及 RA;到了元件階段,可以透過 MOKE 分析磁性,配合 C-AFM 檢測電性;最後晶圓完全產出後,可利用 WAT 做 MRAM 參數分析,磁學模擬也是一項除錯的重要手法,從微磁模擬 (OOMMF) 可以分析元件中磁矩的進動情形,然而卻無法針對非磁性的參數做設定;而從原子層級模擬 (Vampire),可以進一步設定材料參數,如介面粗糙度、晶格常數等等,透過各種量測手法與製程開發,MRAM 開發將更加迅速,有朝一日將更為普及在日常生活中。

誌謝

本研究團隊感謝工研院電光所團隊吳志毅所長、許世玄組長、魏拯華經理、辛毓真小姐對本團隊在 MRAM 研究上之長年支持。